Designed to address the growing demand for faster datacentre links, the DAC combines speed and power efficiency, setting a new standard for wireline data conversion.

The demand for higher data transfer rates in datacentres continues to surge as data-intensive applications like machine learning and AI become more prevalent.

Ultra-fast ADCs and DACs are therefore essential to ensure data flow in next-generation wireline systems. Conventional architectures often fall lopedshort, resulting in signal degradation and power inefficiencies.

At the same time, power efficiency is becoming increasingly important, as the amount of interconnect deployed inside large-scale datacentre infrastructures grows at an even faster pace than the amount of compute.

PAM-4 has emerged as the preferred modulation scheme in datacentres, enabling faster data transfer without requiring more bandwidth.

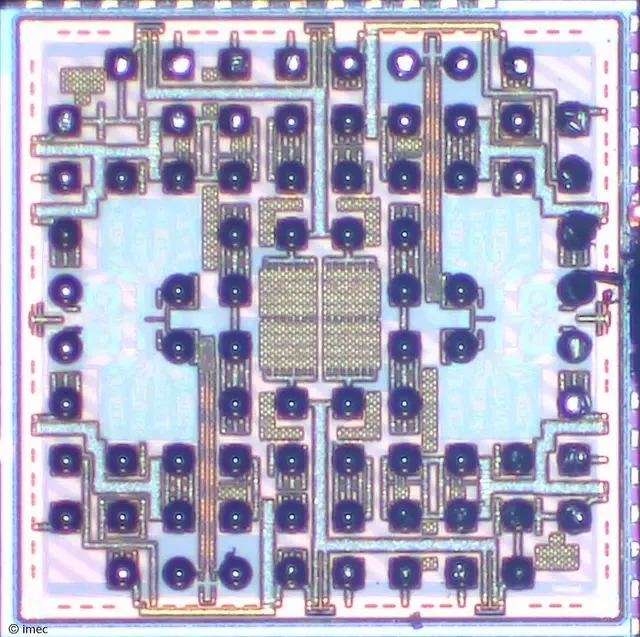

“This 7-bit DAC is designed for next-generation data center links, targeting data rates above 200 Gb/s and ultimately reaching 400 Gb/s per lane. In order to efficiently manage these speeds, the necessary signal processing is implemented in advanced CMOS nodes such as 5nm FinFET. Consequently, the DAC must also be realized within the same technology node. Integrating such complex architectures in scaled CMOS nodes draws on imec’s unique expertise in advanced integrated circuit design,” says Peter Ossieur, programme manager for high-speed transceivers at imec.

To optimize power efficiency, imec has innovated the DAC architecture by drastically reducing the number of unit cells from 127 to 34. This has minimized switching activity, effectively lowering power consumption (to 621 mW at 0.9V and 0.96V supplies) without compromising speed. This reduction also decreases parasitic effects, enabling more accurate signal conversion at higher data rates.

Ossieur added: “Looking ahead, the team aims to address the growing demand for even faster data links by targeting the next generation of ADCs and DACs based on 3nm CMOS technology. The focus is on doubling the sampling rate to 300GSa/s and pushing bandwidth beyond 100GHz. To achieve such speed imec will draw on its expertise in analogue design, and now also addresses the design of ultra-low-jitter clock generation circuitry targeting femtosecond-level accuracies.”