The migration workflow builds on the foundry’s Analog Design Migration (ADM) methodology to streamline the redesign of passive devices and design components to the advanced RF process rules.

The collaborative migration workflow leverages the performance gain of the N4P process for the LNA design migrated from N6RF+, said Keysight. Components include the Synopsys Custom Compiler layout environment with Synopsys ASO.ai for rapid analogue and RF design migration. Another components is Synopsys PrimeSim circuit simulator, and Keysight’s RF Circuit simulation tool, RFPro, for device parameterisation, automated value fitting, and electromagnetic (EM) simulation.

The company said that using AI accelerates the RF circuit migration process and redesign using Synopsys Custom Compiler with AI-driven analogue design migration tool, ASO.ai, to identify optimal design parameters to meet performance metrics. The combination also optimises a design’s PPA (power, performance, area).

Keysight RFPro is for the parameterisation of passive devices, including inductors. It automatically re-creates simulation models with layouts tuned to the new process rules.

According to Niels Faché, senior VP of Keysight’s Design Engineering Software division, “Meeting PPA requirements while adhering to new process design rules is one of the biggest challenges facing complex RF chip designs. RF circuit designers want to leverage and reuse their libraries of N6RF+ devices and component IP to improve ROI”. He said that combination which models within TSMC’s ADM methodology means there no “time-consuming data handoffs or domain specialisation are required, which increases overall engineering productivity for RF circuit designers.”

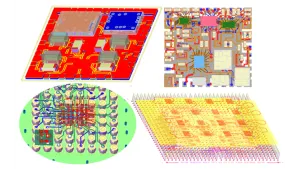

At DAC 2025, Keysight was highlighting the first release of RFPro which provides multi-physics simulation support for RFIC designers working in Cadence Virtuoso and Synopsys Custom Compiler.

It includes Winslow nonlinear amplifier stability analysis, modulated signal analysis with error vector magnitude (EVM) optimisation and supports mixed hierarchies for 3D heterogeneous integration and chip packaging (pictured).

The flexible licensing allows multiple types of simulations simultaneously which can be shared across multiple users.

Related news: