For the first time, high aspect ratio (AR=6) processing of ruthenium (Ru) in a semi-damascene fashion is experimentally shown to result in about 40% resistance reduction without sacrificing area. Additional simulations confirm the benefits at circuit level in combination with airgaps as dielectrics.

A complementary experimental study shows that the reliability of semi-damascene with airgaps is competitive when compared to dual-damascene with low-k dielectrics.

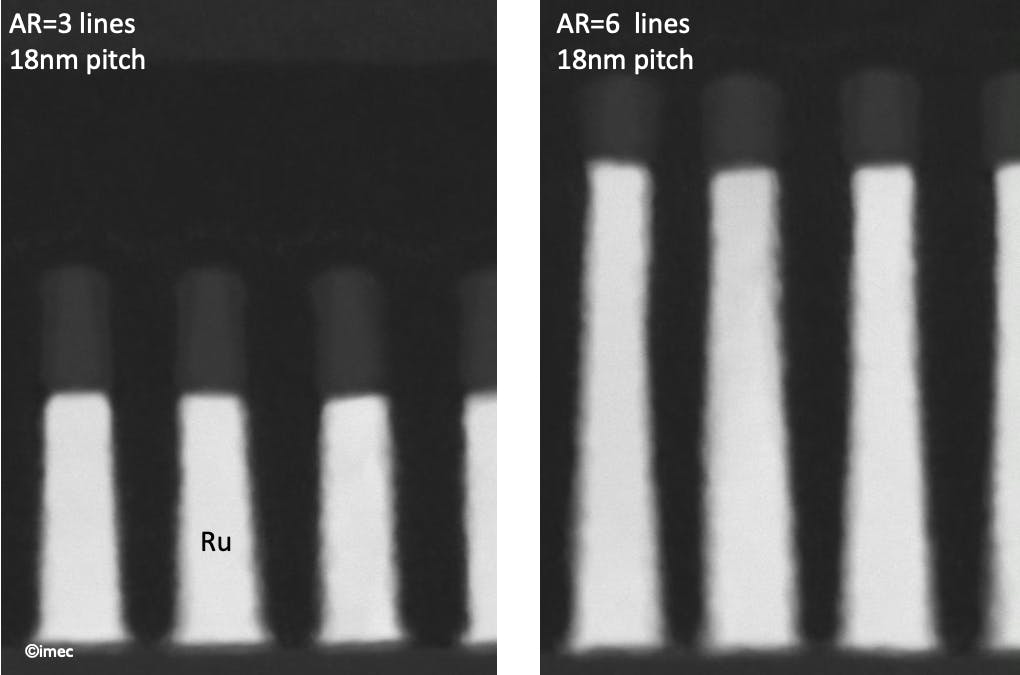

After providing the first experimental demonstration of a functional two-metal-level semi-damascene module at 18nm metal pitch, AR=3, with fully self-aligned vias at VLSI 2022, imec proposes to extend this integration scheme to further reduce the line resistance of the Ru interconnects, while keeping the same footprint.

This can be achieved by high-AR processing of the Ru lines using an advanced subtractive metal etch process.

Zsolt Tokei: “We measured a significant line resistance reduction of about 40% on Ru lines with AR=6 compared to lines with conventional AR=3. In addition, we showed the benefits at circuit level of implementing high-AR semi-damascene lines with airgaps.” In a benchmark study, imec also demonstrated that the semi-damascene flow with airgaps is reliable with more than 10 years lifetime.

“With no less than 10 oral presentations at this year’s IITC, addressing the main challenges in interconnect scaling, imec has a proven path to push the interconnect roadmap for the coming ten years,” concludes Zsolt Tokei, “The papers cover advances in semi-damascene integration as a promising interconnect scheme for future logic nodes, memory technologies and highlight progress in middle-of-line (MOL) metallization schemes, dielectrics, alternative metals exploration, and reliability.”