This said, Delft University of Technology, working with Goodix Technology, seems to have got right up amongst the hi-fi numbers with a 0.18μm BCD prototype IC that achieves 120.9dB dynamic range and -111.2dB peak THD+N.

At full power (10% THD) it can deliver 13W into 8Ω with 90% efficiency, or 23W into 4Ω at 86%.

Ironically, despite having a digital input, it resorts to an analogue signal deep in its heart.

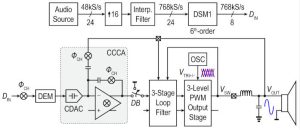

At the front end a capacitive DAC is used to avoid the thermal and 1/f noise found with current-steering or resistive DACs.

This drives a closed-loop Class-D amplifier based on a capacitively-coupled chopper-amplifier topology.

As the DAC output contains DAC images around multiples of the sampling frequency, as well as shaped quantisation noise, attention is paid to the frequency plan to prevent inter-modulation between the DAC output and the various chopping and PWM tones.

The 24bit input is up-sampled to 768kHz (16×48kHz), reduced to 8bit by a digital ΔΣ modulator, then the DAC converts it to analogue for the chopper amplifier and the rest of the Class-D amplifier, which has a 4.992MHz three-level PWM output running from a 14.4V rail. This frequency is the 13th harmonic (therefore odd) of the chopping frequency, avoiding intermodulation of the sidebands.

“However, this also means that PWM frequency is not located at a multiple of samplig frequency [it is 6.5x], so some quantisation noise folding will occur,” said Delft. “Fortunately, the quantisation noise around the PWM frequency is attenuated by the sinc roll-off of the DAC spectrum and the low pass characteristics, so the folded noise is negligible.”

The prototype is 7.5mm2 with the interpolation filter and digital ΔΣ modulator in a separate FPGA.

Problems of using chopper amplifiers in high-dynamic-range operational amplifiers

The next paper in that ISSCC session, also by Delft University of Technology, looked deeply into the problems of using chopper amplifiers in high-dynamic-range operational amplifiers, due to the input and output switches transitioning simultaneously while the signal takes a finite time to pass through the amplifier.

This leads to slightly mis-timed chopping at the output, causing spike-like output errors.

Using two parallel chopper amplifiers, chopped in quadrature, and selecting their outputs alternately, away from the chopping moments, can eliminate these spikes.

Delft instead used one original-quality chopper amplifier, then only used the parallel amplifier briefly around the chopping point of the main amplifier, allowing the 1/f noise and offset specs of the parallel amplifier to be slackened with no drop in overall quality, and te secondary amplifier can be turned off for most of the time to save power.

This team built the amplifier on 0.57mm2 of a 0.18μm BCD process, where it consumes 620μA from 5V, dropping to 530μA when the secondary amplifier is selected.

With the op-amp wired as a buffer, a single 1Vrms 79kHz (~4x Fchop) input evokes a -125.7dB IMD tone at 1kHz (4xFchop – Fin), which is much worse at -102dB if the main amplifier is uesd 100% of the time.

The figures at 39kHz Fin (~2x Fchop) are -128.5dB worsening to 112.8dB.

At Fin <5kHz, IMD tones are below the -140dB noise floor.

Input current is 22.6pA max.

ISSCC 2023 paper 3.1 A 120.9dB DR, -111.2dB THD+N digital-input capacitively-coupled chopper Class-D audio amplifier

ISSCC 2023 paper 3.2 A Chopper-stabilized amplifier with a relaxed fill-in technique and 22.6pA input current

The IEEE International Solid-State Circuits Conference, held annually in San Francisco, is a world showcase for IC-based analogue, digital and RF circuity. It offers an opportunity for IC and circuit design engineers to maintain technical currency, and to network with experts.